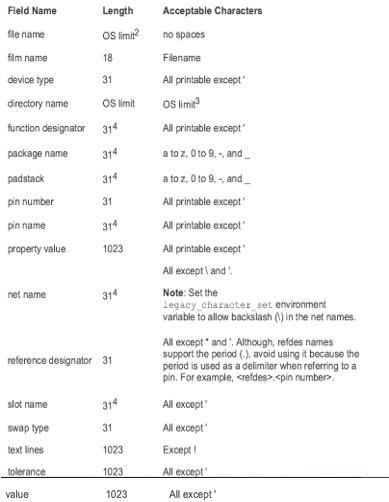

有關零件屬性的一些限制及說明

適用版本:17.2以上

OrCAD Capture在零件屬性中的命名以及數值有一些限制,若違反了這些限制,在輸出Netlist時就會造成錯誤。

1.…

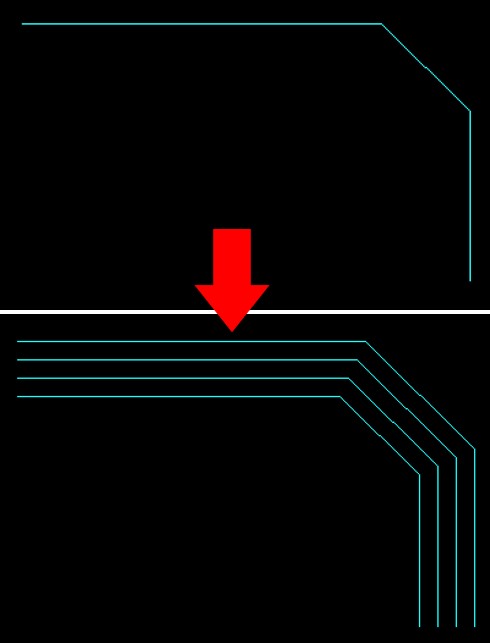

如何新增等距的平行線段

適用版本:16.6以上

當我們在Allegro的Board中,會遇到BUS線路上要設定等距且大於DRC設定時,我們可以利用Drafting的功能,方便快速新增線段。

Step1:…

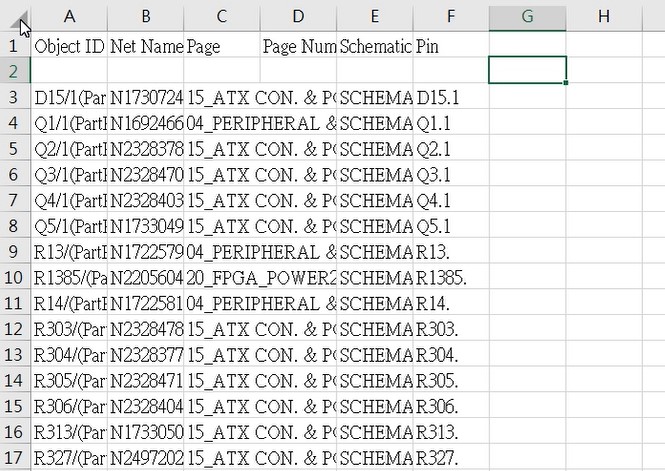

如何快速查詢 Net 與 pins連接關係並將搜尋的結果輸出至Excel

適用版本:17.2以上

在線路圖中,線路非常繁雜,有時候我們會需要確認線路與Pins之間的連接關係,那我們該如何快速找出Net與Pins的連接關係呢。

Step1:…

如何設定功能鍵直接指定線寬

適用版本:16.6以上

拉線時,需要另外再做線寬設定,這時,如果可以在拉線時直接指定線寬,就能夠省下很多時間。

Step1:…

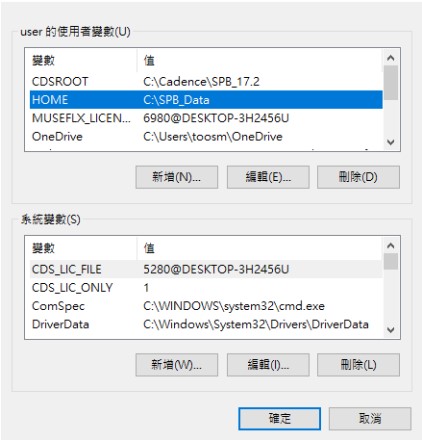

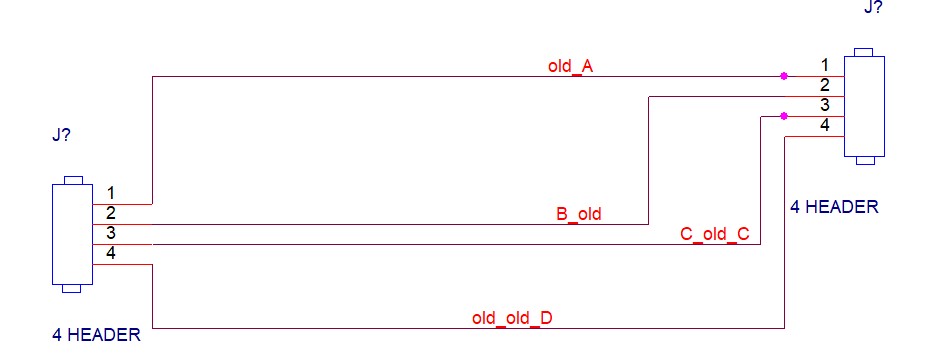

如何整批置換Net names

適用版本:17.2以上

當我們要修改線路圖中的Net…

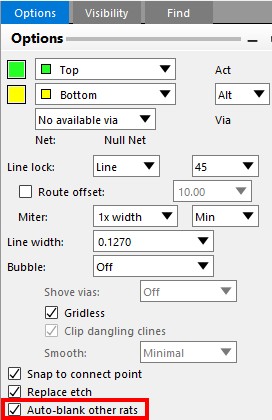

如何在走線時暫時隱藏其他鼠線

適用版本:16.6以上

走線時,若鼠線過多,會造成線路相當複雜不容易看清楚,可以透過暫時隱藏鼠線的方法,避免線路複雜而連接出錯。

在Add…

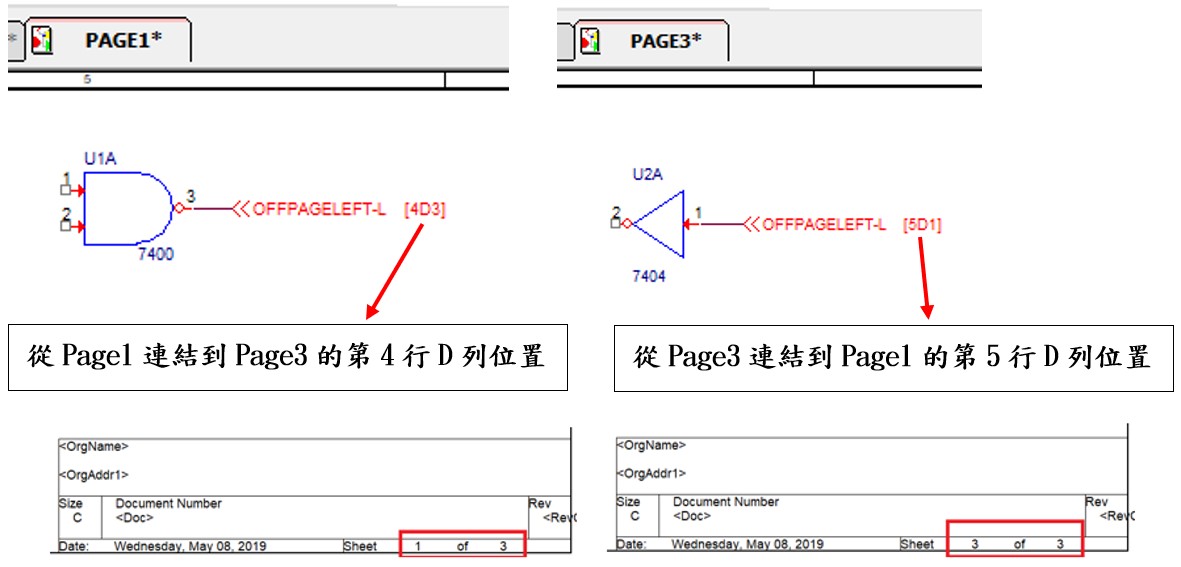

Off-page connector 如何添加位置及頁碼

適用版本:17.2以上

線路設計時,因圖紙頁面的限制,而需要利用跨頁連接的方式來繪製線路圖,這時我們會需要知道連結的位置及頁面。

Step1:…

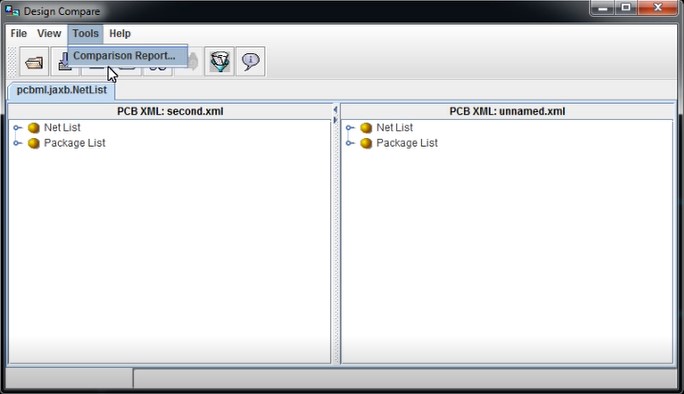

如何檢查線路圖與Board之間,Netlist的一致性

適用版本:17.2以上

當我們要檢查線路與Layout間的Netlist是否一致,我們可以透過Design…

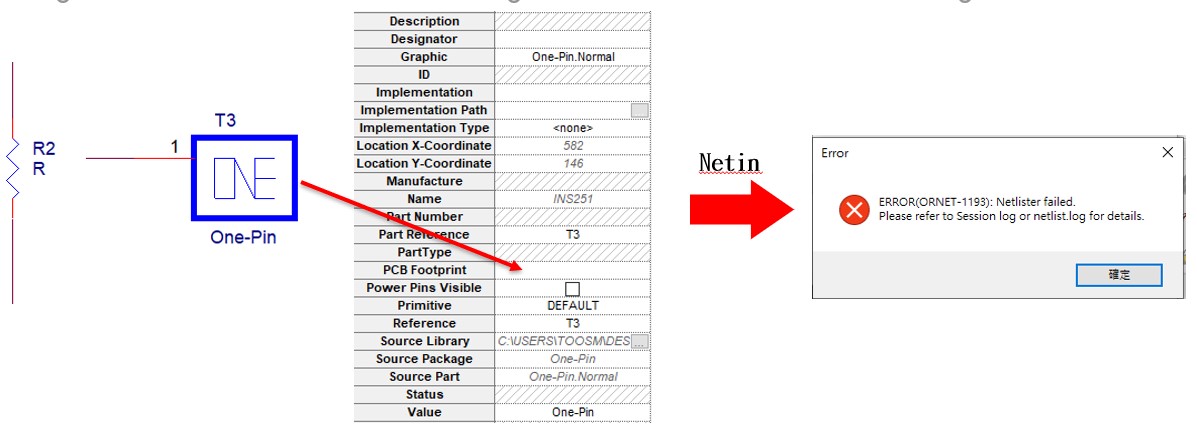

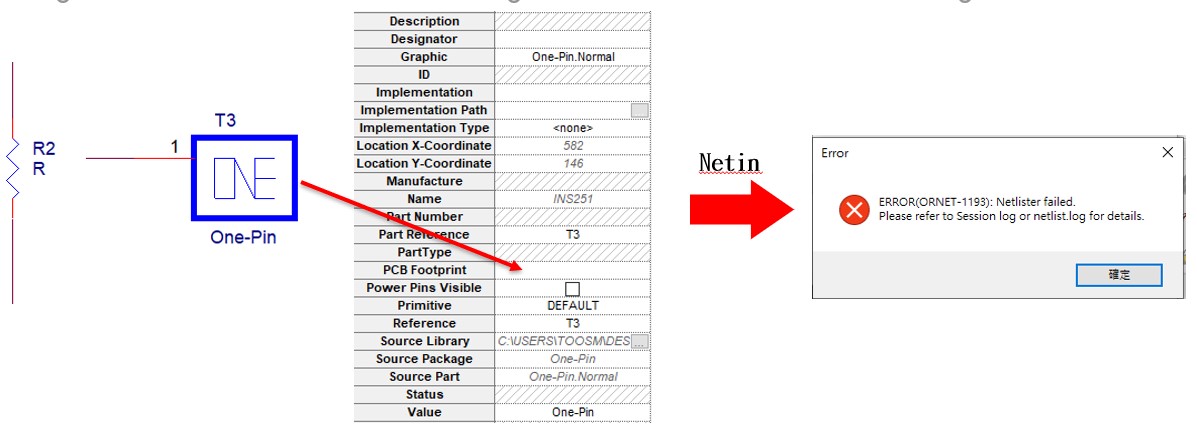

幾種Pin和Footprint在Netin時會發生的情況

適用版本:17.2以上

當我們在線路圖放了一些不需要進Layout但BOM表需要顯示數量的零件,要用什麼方法,來達到這個目的?…

設定DFA_BOUND重疊時報DRC

適用版本:17.2以上

當我們有DFA_Bound相互重疊時,不會產生DRC,會自動切換為Place_Bound來檢查。

Step1:…