Cadence發表業界首款小晶片和先進封裝3DIC平台 加速系統創新

Cadence Design Systems今天宣布,正式推出CadenceO Integrity 3D-IC平台,為業界首個全面、高容量的3D-IC平台,將設計規劃、實現和系統分析,整合在單個且統一的管理介面上。此一整合型3D-IC平台,可支援Cadence第三代3D-IC解決方案,通過熱完整性、功率和靜態時序分析能力,提供以系統級PPA表現,使之在單一小晶片(chiplets)中發揮效能。

超大規模運算、消費性產品、5G 通訊、行動裝置和汽車應用,相較於晶粒無法接續的實現方法,晶片設計人員可利用Integrity 3D-IC平台,以達到更高的生產力。該平台的獨特性,能夠提供系統規劃、整合式電熱、靜態時序分析和物理驗證流程,從而實現更快、更高品質的3D設計收斂。

它還結合了3D探索流程,利用2D設計網表,根據用戶的輸入項目,創建多個3D堆疊場景,自動選擇最佳及最終3D堆疊配置。此外,平台資料庫也能夠支援所有3D設計類型,讓工程師可以同步在多個流程節點進行設計,並與封裝設計團隊、以及使用 Cadence AllegroO 封裝技術的半導體組裝/測試外包(OSAT) 公司,進行無縫協同設計。

Cadence資深副總裁暨數位與簽核事業群總經理滕晉慶(Chin-Chi Teng)博士表示:「Cadence 長期透過其領先的數位、類比和封裝實現產品,為客戶提供強大的 3D-IC封裝解決方案。隨著近來先進封裝技術的不斷發展,我們看見客戶的強烈需求,就是必須進一步在我們已然成功的3D基礎上,提供一個更緊密的整合型平台,將我們的設計實現技術與系統級規劃分析連結在一起。隨著產業不斷推進開發差異化的3D堆疊晶粒配置,全新的Integrity 3D-IC平台讓客戶能夠實現以系統驅動的功率、性能和面積 (PPA),降低設計複雜性,加速產品上市。」

Integrity 3D-IC平台是Cadence 廣泛的3D-IC解決方案系列產品中的一員,此一系列產品組合在原有數位產品之外,增添了系統、驗證以及矽智財功能。此一更加多元的解決方案通過由 Palladium Z2 和 Protium X2 平台組成的 Dynamic Duo,提供整個系統的軟硬體協同驗證和功率分析。該平台支援基於小晶片技術的埠實體層矽智財,和專門將延遲、頻寬和功率的PPA進行優化。

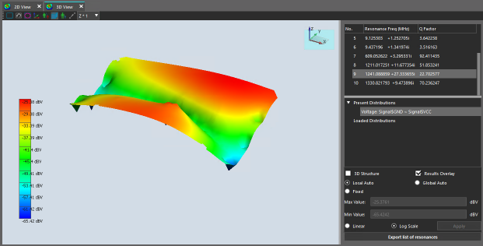

Integrity 3D-IC平台提供協同設計的可行性,讓Virtuoso 設計環境和Allegro 技術,整合性晶片簽核提取和具有 Quantus 提取解決方案與 Tempus時序簽核解決方案的靜態時序分析,以及整合訊號完整性/電源完整性 (SI/PI) 、電磁干擾 (EMI) 和Sigrity技術系列熱分析,Clarity 3D 瞬態求解器和Celsius 熱求解器等等,都有具有共同設計的功能。全新的Integrity 3D-IC平台和更多元的3D-IC解決方案系列組合,都建立在系統單晶片卓越設計和系統級創新的堅實基礎上,支援公司的智慧系統設計策略( Intelligent System Design)。

使用Integrity 3D-IC平台的客戶可以獲得以下功能和優勢:

- 統一個管理介面和資料庫:讓SoC和封裝設計團隊同時的協同優化整個系統,從而有效地整合系統級反饋。

- 完整的規劃平台:為所有類型的3D設計整合出完整的3D-IC堆疊規劃系統,使客戶能夠管理和實現本質的3D堆疊。

- 無縫設計實現工具的整合:採用Cadence Innovus?實現系統的通過腳本直接整合,為3D晶粒分區、優化和時序流的大量數位設計,提供易用性。

- 整合系統級分析能力:通過早期電熱和跨晶粒靜態時序分析,設計出穩健的3D-IC設計,從而為以系統驅動的功率、性能和面積 (PPA) 提供早期系統級反饋。

- 與 Virtuoso 設計環境和 Allegro封裝科技進行協同設計:允許工程師採用分層資料庫,將設計資料從 Cadence 類比封裝環境,無縫地移動到系統內的其他部分,從而加快設計收斂,提高生產效率。

- 易於使用的介面:包括一個功能強大的用戶管理介面和流程管理器,為設計人員提供了一致、具互動性的方法,來運行有關的系統級3D系統分析流程。