Sigrity SI 進階電源效應的平行匯流排的建模、模擬與分析課程

課程名稱: 進階電源效應的平行匯流排的建模,模擬與分析

Modeling, Simulation, and Analysis of Power-Aware Parallel Bus Systems

天 數:1天

課程大綱:

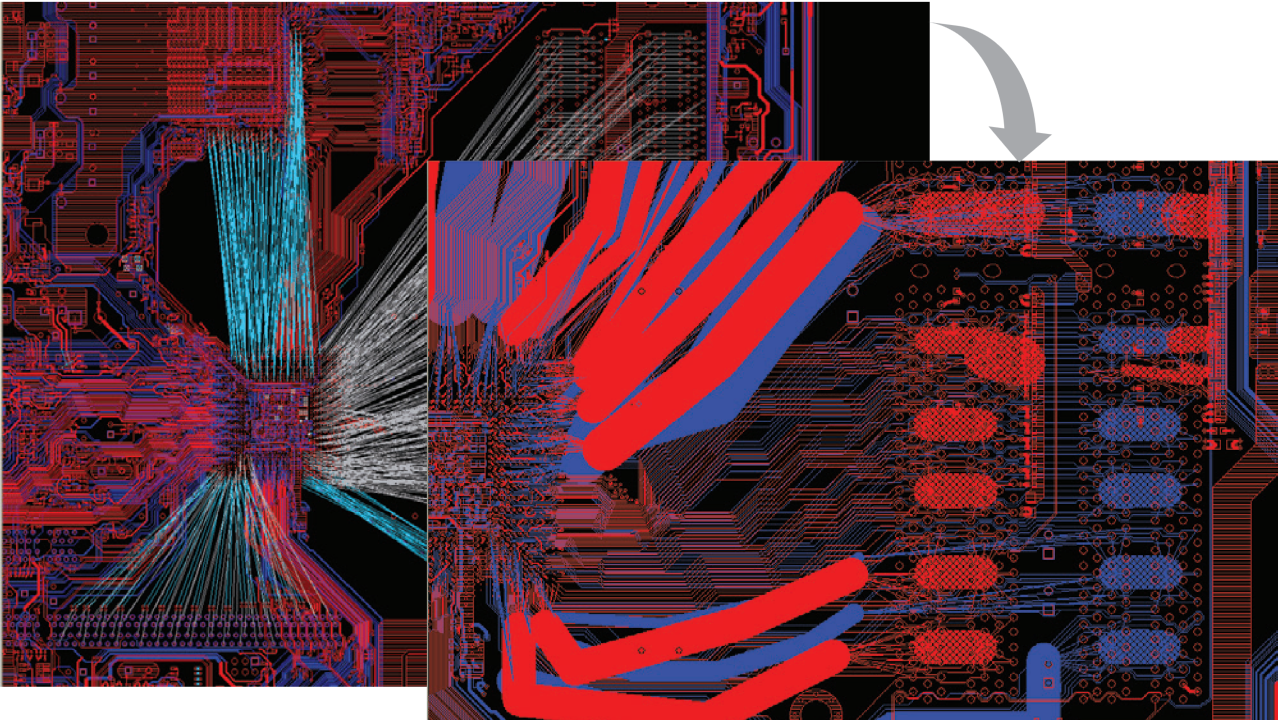

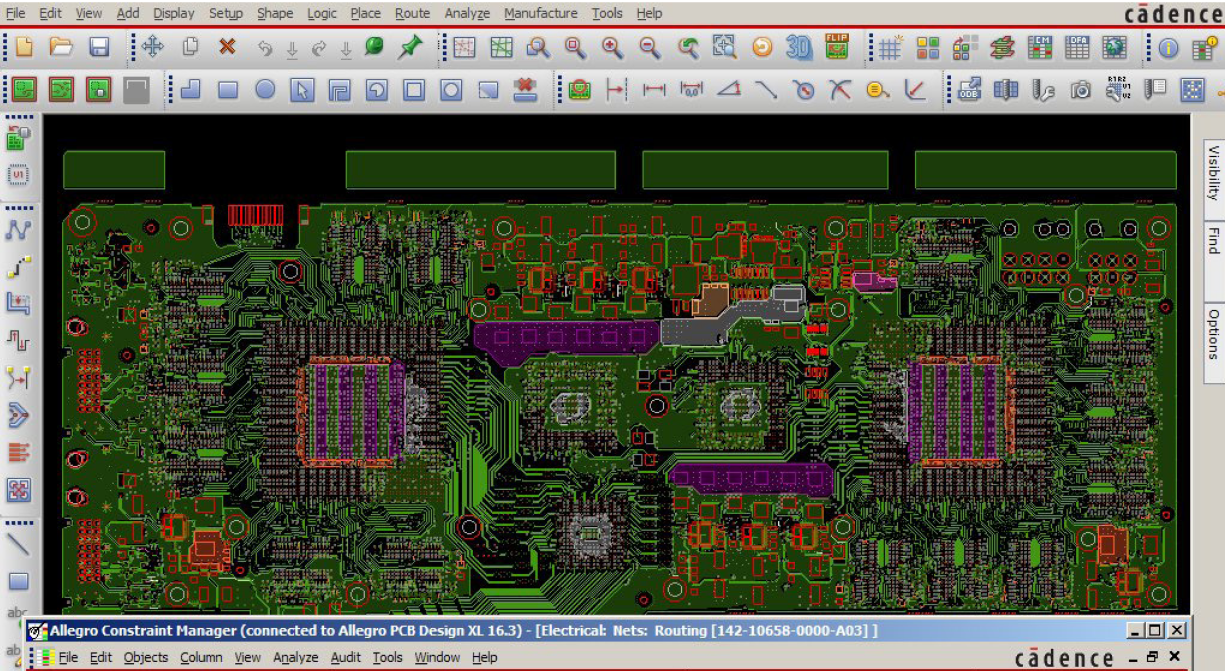

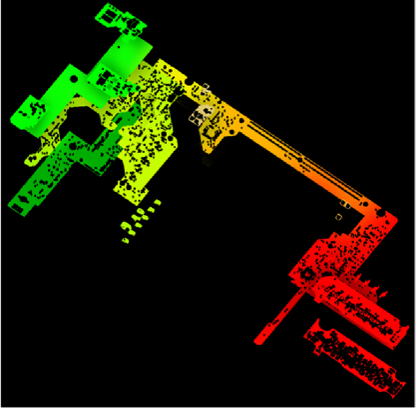

- Build power-aware bus system models with the S-parameters model

用S參數模型建立有電源效應的匯流排系統模型

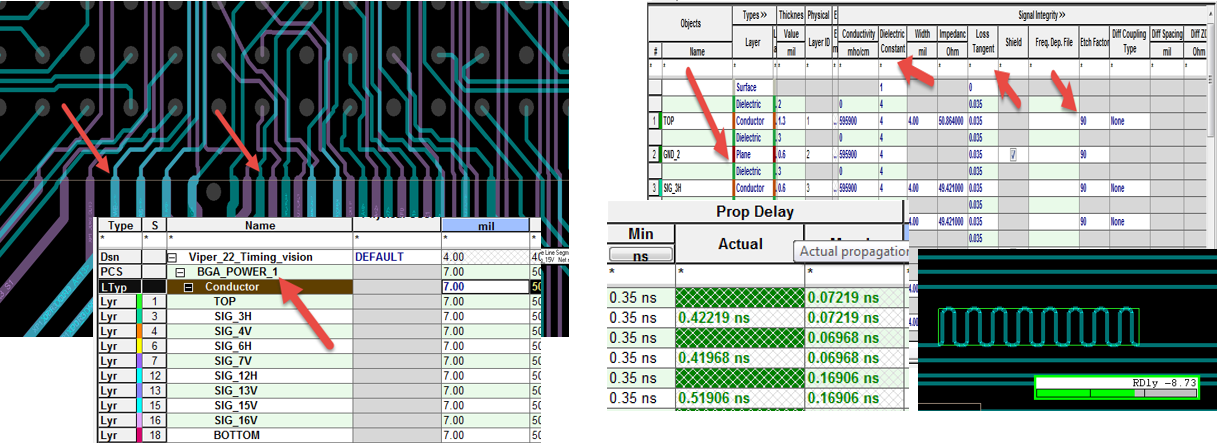

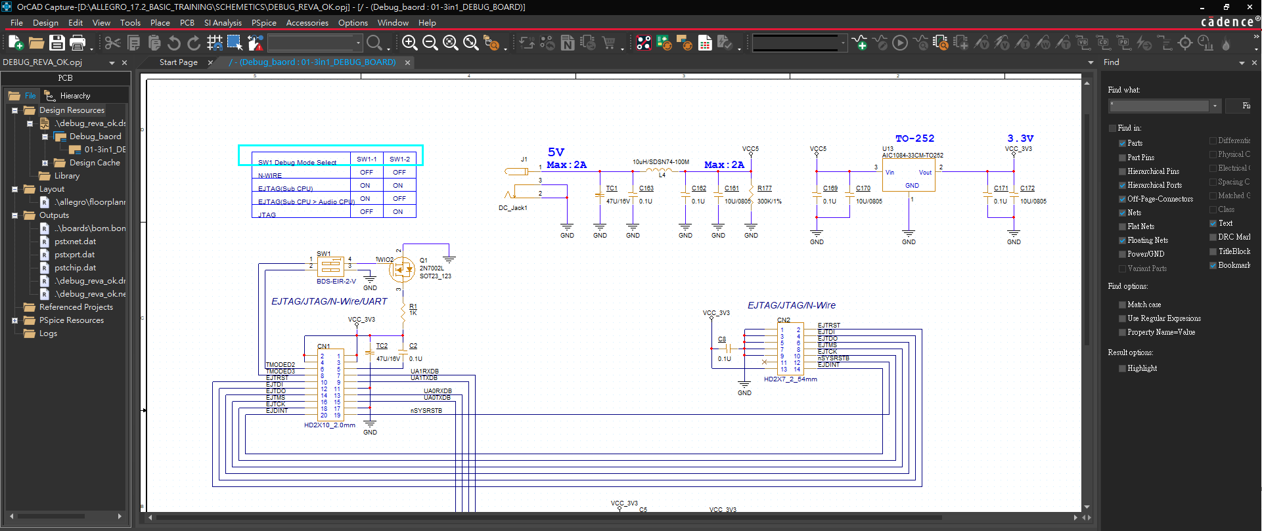

- Connect blocks of the DDR models and check signal connectivity between blocks of these systems.

連接DDR block模型與確認系統方塊間的信號連接

-

Set timing budget and analysis options for these systems, including channel simulation options for the DDR-PAPBS.

設定DDR的分析選項與時間預算

- Run simulations of the DDR-PAPBS with or without ideal power,

用理想與非理想電源做DDR的模擬.

-

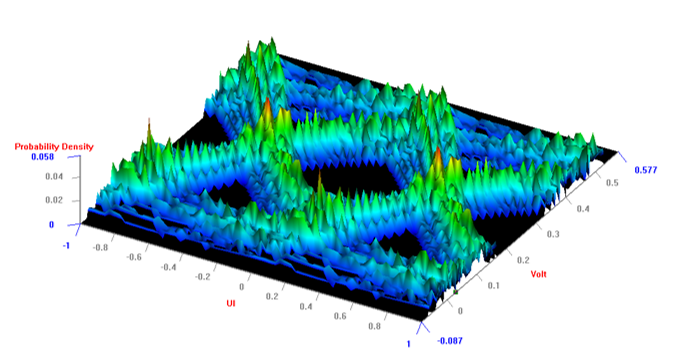

Generate simulation-based reports and results in terms of 2D voltage plots of data and strobe signals, and data Eye diagrams.

產生模擬結果與分析報告,包括2D波形與眼圖

-

Analyze simulation based results and tables to evaluate power and signal integrity performance of the DDR3-PAPBS.

分析DDR電源與信號完整度的效益

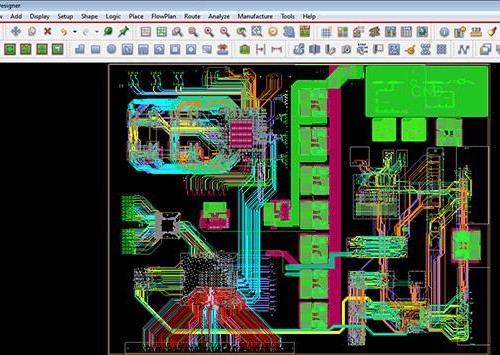

- Replace the S-parameters model of the power-aware

置換電源的S參數模型

-

Perform simulation and analysis of the DDR3-PAPBS with sweeping parameters.

用參數掃描來做DDR的模擬分析

-

Run SSN simulations of this modified DDR3-PAPBS by defining “Ranks” of memory.

設定DDR的Rank來做SSN 同步切換雜訊的模擬

- SystemSI DDR5 Simulation: Part 1

用SystemSI對 DDR5做基礎模擬

- SystemSI DDR5 Simulation: Part 2

用SystemSI對 DDR5做進階模擬